Introduction

-A

memory or a data byte, or a word, or a double word, or a quad word may be accessed

from or at all addressable locations with a similar process would be used to access

from all locations and there is would be equal access time for a read or for a

write that is independent of a memory address location. This mode

differentiates from another model called serial access mode.

i ) Memory Hierarchy

Figure 1 : Pyramid Table

- Hierarchical

Memory Organization

|

| Figure 2 |

- How is the

Hierarchy Managed?

·

by compiler (or programmer) .

·

by the cache controller hardware.

·

by the operating system (virtual

memory).

·

virtual to physical address mapping assisted by the hardware(TLB).

·

by the programmer (files).

ii ) Main Memory

Main memory organization

- The main

memory stores instructions and data of the currently executed

programs.

- Sometimes, its part can be implemented as the fixed memory or read-only

memory ROM.

- A main

memory can be built of a single or many memory modules. A main

memory module is built of an address decoder and a set of memory locations. The

locations store words of bits of data assigned to consecutive addresses. The

word can contain any, but fixed for a given computer, number of bits. There can

be several word formats available in the same computer. Usually, the words are

so defined as to contain an integer number of bytes.

- To store one bit of

information, a bit cell is used in main memory. To read or

write a word, an access has to be organized to a sequence of bit cells. The

memory word length in contemporary computers can be a single byte or many

bytes.

- Organization

structures of main memories can be divided, according to the circuit that

selects memory locations, into the following types:

- Main memory with

linear selection (with a single address decoder)

- Main memory with

two-dimensional selection (with two address decoders)

- Main memory with linear selection of multiple words (with a single address decoder and a selector)

- Main memory with linear selection

Figure 3 : The principle of linear selection of memory locations

Figure 4 : Main memory module with linear selection

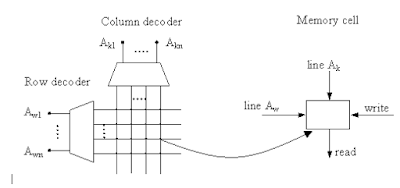

- Main memory with two-dimensional select

Figure 5 : The

principle of two-dimensional selection of memory locations

Figure 6 : Memory

module with a two-dimensional selection of memory locations

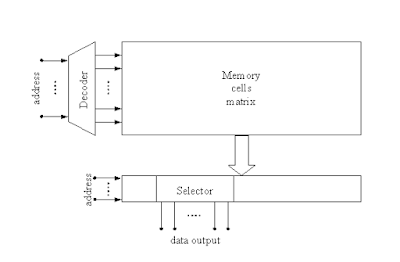

- Main memory with linear selection of multiple words

Figure 7 : Main

memory with linear selection of multiple words

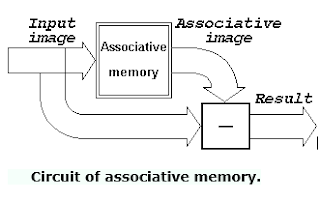

iii ) Associative memory

- Associative memory is found on a computer hard drive and used only in specific high-speed searching applications.

- Most computer memory known as random access memory, or RAM, works through the computer user providing a memory address and then the RAM will return whatever data is stored at that memory address.

- However, CAM works through the computer user providing a data word and then searching throughout the entire computer memory to see if the word is there. If the computer finds the data word then it offers a list of all of the storage addresses where the word was found for the user.

- CAM is faster than RAM in almost every search application, but many people stick with RAM for their computers because a computer with CAM is more expensive than RAM.

-The reason for the price increase for CAM computers is because with CAM computers, each cell has to have the full storage capability and logic circuits that can match content with external argument.

- Associative memory computers are best for users that require searches to take place quickly and whose searches are critical for job performance on the machine.

|

| Figure 8 |

iv) Cache Memory

- A computer can have several different levels of cache memory.

- The level numbers refers to distance from CPU where Level 1 is the closest.

- All levels of cache memory are faster than RAM.

- The cache closest to CPU is always faster but generally costs more and stores less data then other level of cache.

Figure 9 : Different levels of Cache Memory.

Level 1 (L1) Cache

- It is also called primary or internal cache. It is built directly into the processor chip. It has small capacity from 8 Km to 128 Kb.

Level 2 (L2) Cache

- It is slower than L1 cache. Its storage capacity is more, i-e. From 64 Kb to 16 MB. The current processors contain advanced transfer cache on processor chip that is a type of L2 cache. The common size of this cache is from 512 kb to 8 Mb.

Level 3 (L3) Cache

- This cache is separate from processor chip on the motherboard. It exists on the computer that uses L2 advanced transfer cache. It is slower than L1 and L2 cache. The personal computer often has up to 8 MB of L3 cache.

v) Virtual Memory

- A cache stores a subset of the addresss space of RAM. An address space is the set of valid addresses.

- Thus, for each address in cache, there is a corresponding address in RAM. This subset of addresses (and corresponding copy of data) changes over time, based on the behavior of your program.

- Cache is used to keep the most commonly used sections of RAM in the cache, where it can be accessed quickly.

- This is necessary because CPU speeds increase much faster than speed of memory access. If we could access RAM at 3 GHz, there wouldn't be any need for cache, because RAM could keep up. Because it can't keep up, we use cache.

- What if we wanted more RAM than we had available. For example, we might have 1 M of RAM, what if we wanted 10 M? How could we manage?

- One way to extend the amount of memory accessible by a program is to use disk. Thus, we can use 10 Megs of disk space. At any time, only 1 Meg resides in RAM.

- In effect, RAM acts like cache for disk.

- This idea of extending memory is called virtual memory. It's called "virtual" only because it's not RAM. It doesn't mean it's fake.

- The real problem with disk is that it's really, really slow to access. If registers can be accessed in 1 nanosecond, and cache in 5 ns and RAM in about 100 ns, then disk is accessed in fractions of seconds.

- It can be a million times slower to access disk than a register.

- The advantage of disk is it's easy to get lots of disk space for a small cost.

Still, becaues disk is so slow to access, we want to avoid accessing disk unnecessarily.

Figure 10

iv ) Memory Management Hardware

- A memory

management system is a collection of hardware and software procedures for

managing various programs (effect of multiprogramming support) residing in

memory.Basic components of memory management unit (MMU) are:

o

A facility for

dynamic storage relocation that maps logical memory references into physical

memory addresses.

o

A provision for

sharing common programs by multiple users.

o

Protection of

information against unauthorized access.

- The dynamic

storage relocation hardware is a mapping process similar to paging system.

- Segment:It is more

convenient to divide programs and data into logical parts called segments

despite/fixed-size pages. A segment is a set of logically related instructions

or data elements. Segments may be generated by the programmer or by OS.

Examples are:a

subroutine, an array of data, a table of symbols or user’s program.

- Logical

Address:The address generated by the segmented program

is called alogical address.This is similar to virtual address except

that logical address space is associated with variable-length segments rather

than fixed-length pages.

Segment Page

Mapping

- The length of

each segment is allowed to grow and contract according to the needs of the

program being executed. One way of specifying the length of a segment is by

associating with it a number of equal-sized pages.

Figure 11 : Logical to physical address mapping

Logical address = Segment+page+Word

- Where segment specifies segment number,page field specifies page within the segment and word field specifies specific word within the page.

- Here, mapping of logical address to physical address is done by using two tables:segment and page table. The entry in the segment table is a pointer address for the page table base,which is then added to page number(given in logical address).

- The sum point to some entry in page table and content of that page is the address of physical block. The concatenation of block field with the word field produces the final physical mapped address.

0 comments:

Post a Comment